Nhà sản xuất chip bán dẫn lớn nhất thế giới TSMC vừa chính thức công bố tiến trình chip 2nm mới với tên gọi N2. Không chỉ cải thiện hiệu năng so với các tiến trình trước, N2 còn hướng tới việc tiết kiệm đáng kể điện năng tiêu thụ khi sử dụng. Dưới đây là tất cả những gì TSMC tiết lộ về đứa con mới của mình.

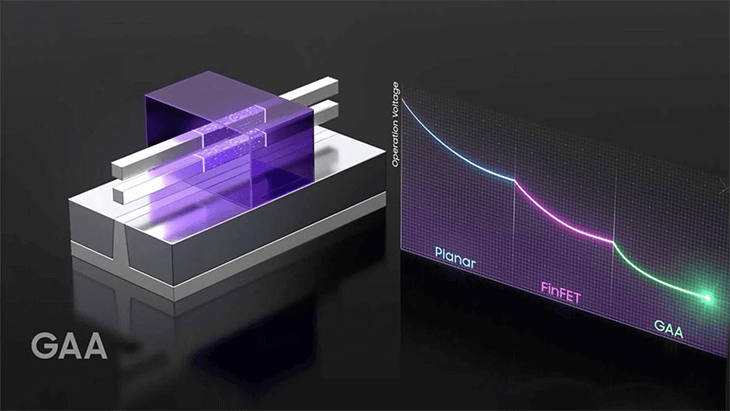

Theo đó, N2 sẽ là tiến trình đầu tiên của TSMC sử dụng bóng bán dẫn GAAFETs (gate-all-around field-effect transistors) và sẽ tăng mật độ chip lên khoảng 1,1 lần so với N3E, thế hệ 3nm được ra mắt ngay trước đó. Dự kiến TSMC sẽ tung ra các sản phẩm áp dụng tiến trình 3nm trước khi đưa N2 ra ánh sáng.

Tiến trình 3nm sẽ có 5 phiên bản với số lượng bóng bán dẫn tăng dần lên, qua đó hiệu năng và tính hiệu quả cũng sẽ tăng lên tương ứng. N3 sẽ là cái tên đầu tiên lên sóng, sau đó sẽ là N3E (phiên bản nâng cấp), N3P (nâng cấp hiệu năng), N3S (tăng cường mật độ bóng bán dẫn) và cuối cùng là N3X với “hiệu năng cực đại” theo lời của TSMC. Dự kiến tiến trình 3nm sẽ được nhà sản xuất Đài Loan cho ra mắt vào nửa cuối năm nay.

Trong khi đó, dù còn rất lâu nữa tiến trình 2nm mới ra mắt, tuy nhiên ngay từ lúc này TSMC đã đề ra mục tiêu rõ ràng cho đứa con mới của mình: tăng hiệu năng trên mỗi watt, qua đó tăng cả hiệu năng lẫn các chỉ số về hiệu quả sử dụng. Đồng thời, kiến trúc GAA như đã nói ở trên sẽ giúp hạn chế khả năng rò rỉ hiệu năng, đồng thời cũng có thể tối ưu hóa điện năng tiêu thụ bằng cách thu nhỏ các channel.

Đương nhiên cả N3 và N2 đều có mức tăng đáng kể về hiệu năng so với N5, tuy nhiên một điểm chung nữa là các tiến trình mới này đều chú trọng vào việc tiết kiệm điện năng. Theo những thông tin từ Tom’s Hardware, N3 sẽ tăng khoảng 15% hiệu năng và so với N5, đồng thời tiết kiệm khoảng 30% điện năng khi chạy cùng tần số. Những con số tương ứng của N3E sẽ là 18% và 34%.

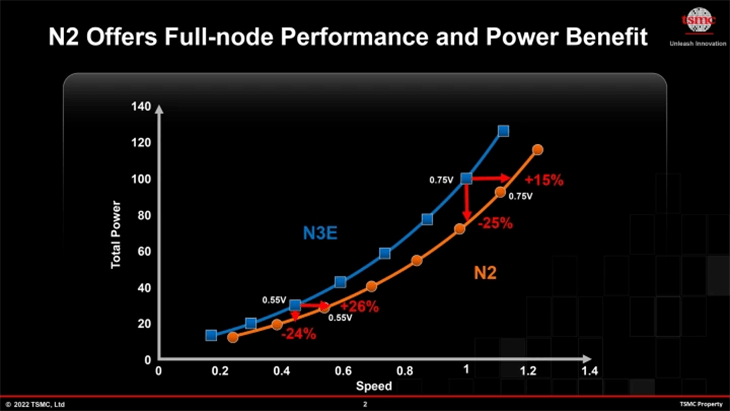

Với những con chip N2, hiệu năng của chúng tiếp tục cải thiện 15% so với N3E khi có cùng mức điện năng. Nếu như giảm về cùng mức tần số với N3E, chip N2 có thể tiết kiệm điện năng hơn tới 30%. Tất cả những con số trên cho thấy TSMC đang hướng tới việc thiết kế những sản phẩm toàn diện hơn, không chỉ chạy đua về hiệu năng thuần mà còn chú trọng vào tính kinh tế của người dùng nữa.

Dự kiến N2 sẽ được trang bị trong tất cả các loại chip từ SoC, card đồ họa mới và những bộ vi xử lý cao cấp. Đồng thời, TSMC cũng tiết lộ thêm rằng quy trình 2nm mới cũng sẽ có tính năng “tích hợp chiplet”. Điều này ngụ ý rằng các nhà sản xuất có thể sử dụng N2 để tối ưu hóa kiến trúc multi-chiplet để nâng hiệu năng lên mức khủng hơn nữa.

Hiện tại, TSMC dự kiến sẽ cho ra mắt N2 vào năm 2025, sau đó đẩy mạnh sản xuất hàng loạt và sẽ phổ cập tiến trình mới vào năm 2026. Dù sao đi nữa, tất cả những mốc thời gian trên vẫn còn khá xa và không loại trừ khả năng nhà sản xuất tới từ Đài Loan sẽ có sự điều chỉnh trong kế hoạch của mình.

Đừng quên ghé thăm TNC News để cập nhật tin tức và những mẹo bổ ích về các sản phẩm công nghệ nhé!

Tin liên quan

Sản phẩm đã xem

Showroom: 172 Lê Thanh Nghị, Phường Đồng Tâm, Quận Hai Bà Trưng, Hà Nội

Tel: (024) 36288790 / (086) 830.2123

Trung tâm bảo hành: 172 Lê Thanh Nghị, Phường Đồng Tâm, Quận Hai Bà Trưng, Hà Nội

Tel: (098) 978 1468

Trụ sở (Không bán hàng): 11 Vũ Thạnh - Cát Linh - Đống Đa - Hà Nội

Tel: (086) 8302123

Fax: (024) 36288790